| NES on FPGA | 16:34 2005/12/30 |

sfl2vl、sfl2vhを使ってみる

「SFL2VHDLよりも変換後のゲート数が削れる」 とのことで紹介していただいたsfl2vl、sfl2vhを使ってみました。 ここでは、今までのコンパイル環境をそのままに、 変換コマンドをSFL2VHDLからsfl2vlへ変更した場合のコンパイル結果を置いています。 またsfl2vlの使い方がまだへたれということもあります。 よって、他の場合に必ずしもこの傾向が出るとは限りませんのでご了承ください。

手順:SFL記述→(SFL2VHDL、sfl2vl)→Verilog→Xilinx ISE 7.1i WebPACK

Target Device:Spartan-2E 300

PC Spec:CPU 700MHz、Mem 512MB、Win2k、Cygwin

▼ インストール

[sfl2vlサポートページ] より本体アーカイブ(Cygwin版:sfl2vlbin-i386-win32-20051222.tar.gz)を取得。 サポートページにはSFLのチュートリアルなどの解説もありますので参考になります。アーカイブを展開、

tar -xzf sfl2vlbin-i386-win32-20051222.tar.gz -C /特にコンパイルも必要ないので楽にインストールできます。

非商用ライセンス版を使用する場合は、sfl2vl.datを取得し、 C:\WINNT(Windows 2000の場合)へ配置。

▼ sfl2vlでVerilogに変換

変換は、% sfl2vl core.sflにて、カレントディレクトリにcore.vが生成されます。

さらに、-Oオプションで制御信号周りの最適化が行われます。 最適化オプションは商用ライセンス、もしくはライセンスなしの試用でのみ利用可能です。

% sfl2vl core.sfl -Oマイクロプロセッサ実装時にコレがキクのデス。

変換時にsflにおいてmodule名と同じstage名を付与できないのでsflを修正。

instrinやtaskにも同じ信号名を付与できないのでsflを修正。

sfl2vhは変換後のVHDLに対し手動で修正が必要

(Shimizu氏にバージョンアップしていただきました!ありがとうございます)

最新版ではXilinxのXSTにも対応しているが…最適化は甘いようです。

sfl2vlの方が実績があり、 変換後の可読性や最適化能力の向上に力を入れているとのことなのでsfl2vlを使いましょう。

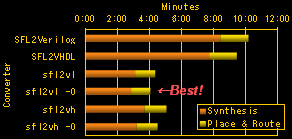

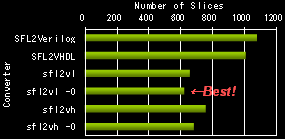

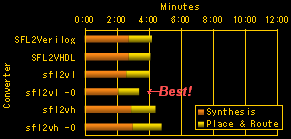

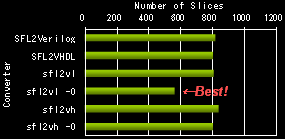

▼ 論理合成と処理時間 2005/11/10

各変換ツールによって得られたHDLは、Xilinx ISE WebPACK 7.1iにて論理合成および配置配線を行います。 このときの処理時間と合成後の回路規模を比べてみました。 論理合成オプションは速度最適化(Normal)を指定しています。 (sfl2vhのデータはおまけと考えてください)

CPU(ログ:

SFL2Verilog、

SFL2VHDL、

sfl2vl、

sfl2vl -O、

sfl2vh、

sfl2vh -O

)

特徴:ひとつのファイルにアドレッシングデコーダべた書き。

従来使用していたSFL2VHDLに比べて、sfl2vl -Oでは、

処理時間が半分に、

回路規模は5分の3まで削減。

速度性能も2割以上アップ。

アドレッシングデコーダが制御信号として大幅に最適化されたのでしょうか?

PPU(ログ:

SFL2Verilog、

SFL2VHDL、

sfl2vl、

sfl2vl -O、

sfl2vh、

sfl2vh -O

)

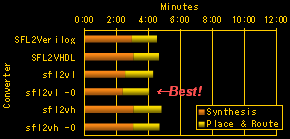

特徴:ひとつのファイルに複数のstageを記述。

他に比べてやはりsfl2vl -Oはちょっといい。速度性能についても向上するようです。

APU(ログ:

SFL2Verilog、

SFL2VHDL、

sfl2vl、

sfl2vl -O、

sfl2vh、

sfl2vh -O

)

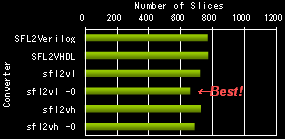

特徴:階層化された複数のモジュールを個別のファイルに記述しています。

sfl2vl -Oによる回路規模削減が飛びぬけているよう。

これまでのところ、のきなみsfl2vl -Oが良い結果をたたき出しているようです。

▼ 実機動作は? 2005/12/30

上記の結果に加え、DMA、PAD、カートリッジI/F、VGA、ステレオユニットなどが含まれます。 しかし最も重要なのが実機動作!動かなければどうしようもないっちゅうわけです。 sfl2vlは実績があるということなので、動かなくても簡単にはこいつのせいにできない!

まずはverilatorの検証も兼ねて、SFL → sfl2vl → Verilog → verilator → C++ にて実行し、

マリオのタイトル画面の描画を確認。

続いて変換したVerilogファイルをxilinxのプロジェクトに取り込んで

XSTで論理合成を試したところ、Verilogのparameter宣言でエラー。

Xilinxのアンサー#9887によると、XSTが対応していないのか。むう。

上位モジュールでVHDLを使用(ソリューション3にあたる)していたためエラーとなっていた模様。

上位をVerilogで記述しなおして合成完了。

FPGA上でも完全に動作しております。 さらに回路規模も20%ほど削減できているので、N106も余裕で追加できます。

▼ んで? (memo)

sfl2vlで、べた書きの(つってもアドレッシングはどうしようもないが)CPUについて 大きな恩恵が得られました。PPUとAPUについても1〜2割は回路規模を削減できています。 sfl2vlを導入すればSpartan3スターターキットにも楽に載りそうです。sfl2vlは、segment記述への対応や簡易なシーケンシャル処理記述などの独自拡張も含めて、 現在もバージョンアップが行われているようです。 個人的にはローカル信号宣言やVHDLのgenericのような使い勝手もほしいところですが、 これらは本質ではない(前処理バッチとして分離できる)し、 もっと本質的な部分にフィードバックをかけるとすると使い倒したいトコロ。 しかし処理系依存の文法を使わないポリシーだとそこは未知の領域…。 うーん、デファクトスタンダードとは…。