| NES on FPGA | 2017/04/29 |

_

▼ オープンソース化!? 2019/06/26

NES on FPGAのSFL+コードをGitHubに公開しました。

今や多くの方がNESをFPGAに実装する取り組みをされていて、 たくさん楽しませていただいたので、今更感がありますが公開することとしました。 ただし他のオープンソースプロジェクトとは異なり、 おそらく閲覧される方はダウンロードしてコンパイルすることは難しいですごめんなさい。

SFL+のプリプロセッサは公開してないですし、 VerilogHDLへの変換はオーバートーン社のNSL Core overtureを申し込んでダウンロードする必要があって、 環境構築のハードルが高いです。 FPGAボードのペリフェラルコードも置いてないですし。

なので、見て頂くだけ。 しかも.sflpとかいう謎拡張子のせいでシンタックスハイライトも不十分だし (無理矢理Cのシンタックスハイライトを付けている)。 こんな感じでいいのかどうなのか。 実際にDE1やDE0のFPGAボードで試してみたい方は、 サイトトップに置いているコンパイル済みのものをお使いください。 ああ、それもGitHubに置いておけばいいのかな。

2020/07/24追記:

何やら“Arctic Code Vault Contributor”というバッジが付いたと思ったら、

公開している2020年2月時点でのコードを北極圏の安全な廃坑にて1,000年保管するプロジェクトだとか。

そしてNES on FPGAおよびSNES on FPGAのSFL+コードについても保管されることになりました。

このバッジが付いた人からは「私の中途半端なコードが1,000年も残るのか」という声がちらほらあり、 私も例にもれずそんな思いではありますが…。 しかし1,000年先の未来でもファミコンやスーファミが語り継がれることになるというのは、 まさにフューチャーノスタルジックなロマンを感じられます。

_

▼ へぇ、専門誌ってこうやって作るんだ 2015/10/10

FPGA特集です!

FPGA特集にたまたまご縁があって [トランジスタ技術2015年11月号] に『ファミコン・サウンド回路と6502互換CPUで懐かしのゲーム音再生』として NSF Player on FPGAについての記事を書かせて頂きました。 初稿ではSFLのコードを掲載するつもりだったのですが、 コードを載せるよりもブロック図の方が分かりやすいのではないか、 ということで矩形波や三角波など各音源のブロック図を載せています。 ファミコン音源を実装しようとしている方への一助になれば。

ターゲットボードは、おそらく持ってる人が多いだろうという理由で、 TerasicのDE0を使用しています。 ただし、NSFファイルを入れておくSDカードは32MB〜1GBのものしかサポートできていないため、 今となっては入手が難しいですがヤフオクかどっかで手に入れてください。 DE0向けのFPGAデータはNES on FPGAのトップページで配布しています。 ぜひNSFを再生してみて、感想を聞かせて頂けると幸いです。

2016年初春追記:

CQ出版社さんから何か届いたと思ったらトラ技CD-ROM版でした。

これって高いんじゃないですか…?

まさか頂けるとは思っていませんでしたよ。

トラ技の韓国版です!

2017年初春追記: さらにCQ出版社さんから何か届いたと思ったら、 今度はトラ技韓国版?の[전자기술 (電子技術)]でした。 ハングル語に翻訳された本記事が掲載されたようで、 他国言語にいつのまにか翻訳されて出版されるというのはなんだか奇妙な感じがしています。

今回は編集さんのご助力もあって良い経験をさせてもらえました。 原稿料も入って新しいFPGAボードが買えそうです。

_

▼ DE1の本家 2012/8/4

DE1ボードのメーカーであるTerasicさんのWebページにある

[Customer Success with Terasic]に

・NES on FPGA

・NES NSF Player on FPGA

・SNES SPC Player on FPGA

がリストアップされました。

なおNES on FPGAのWebページに関しては全編日本語のためリンクされておりません。

情報共有のため英語でお願いしますとのこと。

_

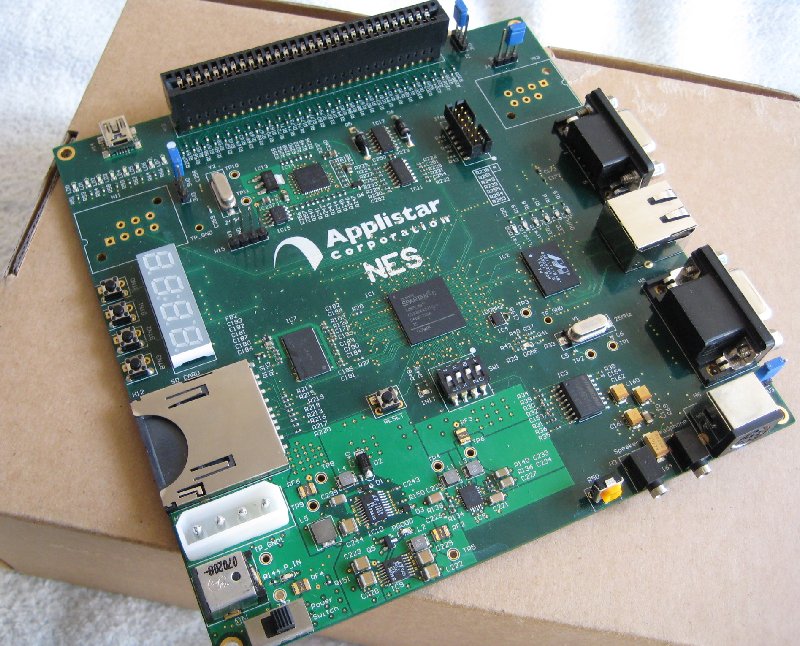

▼ アプリスターさんとこで開発中のNESボード 2012/4/7

FPGAは Spartan-6 LX9 で、NESカートリッジコネクタやDDR2メモリが搭載されています。 技術者教育用に使用しているとのことで、発売については未定。

2022/10/01追記。そういえば動かしてなかったので、

電源アダプタ入手して通電させてみました。

PROMに書かれていたFPGAデータが動いて、

描画が少し不十分だったり音が無かったりするけど、

確かにキーボードでマリオがプレイできました。

_

▼ さすがだな 2007/7

「ひろなex.」1巻より。ひろ兄なにやってはるんですかw

電子工作的なものでマリオ的なものが動いてますね。

_

▼ やっぱり開発者はいない 2005/1/27

なぜか組み込みネットさんに見つかってしまったものたち。

例によってElectronic Design and Solution Fair 2005 with FPGA/PLD Design Conference(EDSF) にてNES on FPGAが展示されました。通常ならば製作者自ら足を運ぶところなのですが、 本拠地でのバックアップも大事だよね!ということでウチでぐうたらしてました。 [組み込みネット写真館:EDSF2005での展示] FPGAの評価ボードにミニチュアファミコンを搭載しました。 カートリッジインタフェースもお出かけ用でカラフルです。 写真の右にはなぜかQROQSのデモ画面が写っています。 便乗ってヤツですね。展示は大変盛況であったとのことで、 説明員をしていただいた方はXilinxさんからSpartan3スターターキットを頂いたそうです。イイナア。

某所から入手した画像

こちらは第8回 組込みシステム開発技術展(ESEC)2005:東京ビッグサイトにて、

FPGA教育用ボードカスタムサービス事例として、ファミコンが搭載されています。

このボードは私の出身大学の演習用に納入したとか。

直接は関わってないのですが、一報ほしかったとですよ。知ってたら足を運んだんですが。

[組み込みネット写真館:第8回ESECプライムシステムズさんの展示]

これってソースコードが出てるんかな。企業の宣伝としてマ○オのデモ流していいのかな〜?

それよりも、実際に教育用としてどういう形でボードを利用してるのか気になるところです。

ベタなところで6502かZ80、さらにオリジナルCPUの実装とコンパイラ製作?

工学部学生ならファミコン程度のシステムくらいは作れると面白いですよ?

_

▼ すべてを信じないで下さい! 2004/10/25

NES on FPGAは、去る2004年10月25日に宮崎のシーガイアにて開催された全九州半導体技術フォーラムで初の実機展示という運びとなりました。 本人は展示をほっぽりだし、旧ダイエーホークス選手陣のキャンプ入りに同行。 シェラトン・グランデ・オーシャンリゾートのツインから望む海岸の夜景は真っ暗で最高でした。

その数日後、ALTERA PLD WORLD 2004にて、アスキーとMSXアソシエーションから 「FPGAでMSXを再現する」の実機展示があったのは皆様すでにご周知のとおり。 この中で、2005年3月を目指して教材にもなるものを発売したいとの横居氏のお言葉。 ALTERA PLD WORLD 2005では、西氏の講演を聴講したり、ブースでMSXステッカーを頂いたりして。 そして2006年12月、ついに「1chipMSX」としてMSXフリークに向けて販売されました。

そこで今回、NES on FPGAについても教材として発売する運びとなりました(嘘)。 今回評価ボードとしてCQ出版のものを使用させて頂いているご縁もあって、 CQ出版社さんからの販売となりました(違)。

| 1chipMSX | NES on FPGA(仮) | |

| 動作展示 | 2004/10/29 | 2004/10/25 |

| 互換機 | MSX | ファミコン |

| デバイス | ALTERA | XILINX |

| CPUコア | Z80 | 6502 |

| 仕様 | オープン | 任天堂 |

| 互換性 | 高 | 中 |

| 出版 | アスキー | CQ出版社 |

| ユーザ | コアユーザ多し | 高い認知度 |

20年の時を越えて再び火蓋が切られようとしております。 いろんな意味でありえませんが。

ちなみに、1chipMSXは約2万円で限定5千台が販売され、 現在プレミアがついているそうですが、 私は予約をキャンセルしてDE1を購入しました。 DE1の方が色々と遊べそうだったので…。