| NES on FPGA | 2007/05/20 |

RAM丒ROM

丂寢壥揑偵偼Spartan-IIE300偵撪憼偝傟偰偄傞BlockRAM偱丄NES偱昁梫側儊儌儕僒僀僘慡偰傪妋曐偡傞偙偲偑偱偒傑偟偨丅 偦傟偧傟偺RAM偼屄暿偵傾僋僙僗壜擻側偺偱暲楍惈傕栤戣偁傝傑偣傫丅

丵

仴 FPGA撪晹僽儘僢僋RAM妱傝摉偰

丂Spartan-IIE300偵偼撪晹僽儘僢僋RAM偑16屄懚嵼偟丄 1儚乕僪8價僢僩偲偡傞偲堦偮偺僽儘僢僋RAM偼512僶僀僩偵側傝傑偡丅

| 梡搑 | 僒僀僘 | 儚乕僪 | 僽儘僢僋RAM悢 | |

| WRAM | 2K僶僀僩 | 8價僢僩 | 4 | 昁 |

| VRAM | 2K僶僀僩 | 8價僢僩 | 4 | 昁 |

| 僗僾儔僀僩RAM | 256僶僀僩 | 8價僢僩 | 1 | 昁 |

| 僷儗僢僩RAM | 32僶僀僩 | 8價僢僩 | 1 | 昁 |

| RGB僇儔乕ROM | 128Word | 16價僢僩 | 1 | |

| 昤夋梡僼儕僢僾僶僢僼傽 | 256Word亊2 | 16價僢僩 | 2 | |

| 僒僂儞僪僨傿儗僀僶僢僼傽 | 256僶僀僩亊2 | 8價僢僩 | 2 | |

| 崌寁 | 15 | |||

丂WRAM丄VRAM嫟偵摨偠僒僀僘偺2K僶僀僩偱偡丅 4偮偺僽儘僢僋RAM傪僇僗働乕僪愙懕偟2K僶僀僩偲側傝丄 傾僪儗僗11價僢僩偺偆偪忋埵2價僢僩偵傛偭偰RAM傪慖戰偟偰偄傑偡丅 僷儗僢僩RAM偼暘嶶儊儌儕乮儗僕僗僞乯偲偟偰攝抲偟偰傕偄偄傒偄偨偄偱偡丅

丂偙傟傜RAM偵偮偄偰偼SFL偱偼側偔VHDL偱婰弎偟偰偄傑偡乮壓婰嶲徠乯丅 悢僶僀僩偺彫婯柾側傕偺偵偮偄偰偼SFL婰弎仺VerilogHDL曄姺偵偰暘嶶RAM偲偟偰儅僢僺儞僌偝傟傞傛偆偵偟傑偡丅

丵

仴 HDL偵傛傞RAM婰弎

丂嵟弶偼Xilinx僨僶僀僗偺僽儘僢僋RAM婰弎傪巜掕偟偨偨傔丄 偙傟傪偦偺傑傑Altera僨僶僀僗傊幚憰偡傞偙偲偑偱偒傑偣傫偱偟偨丅 偦偙偱HDL偵傛傞斈梡揑側RAM婰弎傪彂偄偰偍偔偙偲偱丄 Altera側偳懠偺僨僶僀僗偵傕棳梡偱偒傞傛偆偵偟偰偍偒傑偡丅 [RAM偺婰弎椺] 乮generic傪巊梡偟偰偄側偄偺偼SFL偐傜愙懕偡傞偨傔偱偡丅乯

丂偙傟偼嵟嬤偺榑棟崌惉僣乕儖偺悇榑婡擻傪棙梡偟偨傕偺偱偡丅 HDL偺夝愅偺偲偒偵RAM婰弎傪専弌偟丄 帺摦揑偵僨僶僀僗撪偺僽儘僢僋RAM傗LUT傊儅僢僺儞僌偟偰偔傟傑偡丅 偮傑傝僨僶僀僗偵埶懚偟側偄斈梡揑側RAM婰弎偱丄偳偺儀儞僟偺僨僶僀僗偵傕儅僢僺儞僌偱偒丄 RAM偺僒僀僘傗傾僋僙僗曽朄偵嵟揔側儅僢僺儞僌偑峴傢傟傑偡乮僣乕儖偺惈擻偵傕傛傝傑偡偑乧乯丅

丂傑偨丄僽儘僢僋RAM傪暋悢巊梡偡傞偲偒偵丄僇僗働乕僪愙懕乮512KB亊4乯偡傞傛偆婰弎偟偰偄傑偟偨丅 偙傟傕丄昁梫側僒僀僘乮2048KB乯傪斈梡揑側RAM婰弎偱彂偄偰偍偗偽僣乕儖偑尒慤偭偰偔傟傞偨傔丄 偙偪傜偱僽儘僢僋RAM偺愙懕傪堄幆偡傞昁梫偼偁傝傑偣傫丅

丵

仴 ROM偺弶婜抣愝掕

丂SFL偱偼ROM婰弎偑偱偒側偄偨傔

乮any暥偱婰弎壜擻偱偡偑丄偁傑傝巊偄摴偼側偄傛偆側乧丅VerilogHDL偵曄姺偡傟偽ROM偲偟偰悇榑壜擻丠乯丄

VHDL偱弶婜抣偲偟偰婰弎偟丄

Xilinx偺崌惉偱僽儘僢僋RAM傪僀儞僗僞儞僔僄乕僩乮弶婜壔乯偟偰傕傜偊傑偡丅

[RGB_ROM偺Xilinx岦偗(屆偄)VHDL婰弎椺]

丂偙偺ROM婰弎偵偮偄偰傕丄constant峔暥傪棙梡偟偨斈梡揑側婰弎傪偡傞偙偲偱丄 僣乕儖偺悇榑偵傛傝僨僶僀僗偵儅僢僺儞僌偟偰傕傜偊傑偡丅 [RGB_ROM偺斈梡揑側VHDL婰弎椺]

丂嵟嬤偺sfl2vl偱偼丄mem rom[256]<8> = { 0x12, 0x23, ... }; 偺傛偆側婰弎偱ROM偺弶婜壔偑壜擻偱偡丅 VerilogHDL偵曄姺偡傞偲initial暥偱婰弎偝傟偰傞傛偆側偺偱ROM偵榑棟崌惉偝傟傑偡丅

丵

仴 NSL偱偺mem弶婜壔帪偺拲堄 2018/03/21

丂儗僕僗僞傪偨偔偝傫巊偄偨偄応崌丄偄偪偄偪儗僕僗僞愰尵偡傞偺傕柺搢側偺偱丄 mem婰弎偱愰尵偟傑偡丅

mem pat_reg[4][2];偙傟傪nsl2vl偱VerilogHDL偵偡傞偲丄

reg [1:0] pat_reg [0:3];

always @(posedge m_clock)

begin

if(write)

pat_reg[adrs] <= din;

end

傒偨偄側姶偠偵側傝傑偡丅

拲堄偟偨偄偺偼丄mem偱愰尵偩偗偡傞偲reg偺弶婜壔傕儕僙僢僩傕偝傟側偄偲偄偆帠丅

偙偺偨傔reg偼晄掕抣偲偟偰埖傢傟丄夞楬偵傛偭偰偼嵟揔壔偝傟堄恾偟側偄摦嶌偲側偭偰偟傑偄傑偡丅偍偦傠偟偄両

丂mem愰尵偡傞偲偒偼埲壓偺傛偆偵丄弶婜壔偡傟偽僛儘僋儕傾偝傟傑偡丅

mem pat_reg[4][2] = {0};

nsl2vl偱VerilogHDL偵偡傞偲initial暥偱弶婜抣偑愝掕偝傟傑偡丅

偙傟偼Xilinx傗Intel(媽Altera)偺婰弎僗僞僀儖偱傕悇彠偝傟偰偄傑偡丅

reg [1:0] pat_reg [0:3];

initial begin

pat_reg[0] = 2'b00;

pat_reg[1] = 0;

pat_reg[2] = 0;

pat_reg[3] = 0;

end

丂傕偪傠傫擟堄抣偺巜掕傕壜丅

mem pat_reg[4][2] = {3, 2, 1};

reg [1:0] pat_reg [0:3];

initial begin

pat_reg[0] = 2'b11;

pat_reg[1] = 2'b10;

pat_reg[2] = 2'b01;

pat_reg[3] = 0;

end

RAM弶婜壔偵偮偄偰偺拲堄両 2018/07/30捛婰

丂忋婰偺偲偍傝弶婜壔偡傟偽丄弶婜抣傪帩偨偣偨RAM傪悇榑偝偣傞偙偲偑偱偒傑偡丅 偨偩偟丄偙偺弶婜抣偑桳岠側偺偼FPGA僨乕僞儘乕僪帪偺傒偱丄 悇榑偝傟偨RAM偑儕僙僢僩傪帩偨側偄応崌偼拲堄偑昁梫偱偡丅 偮傑傝弶婜抣偐傜彂偒姺偊傜傟偨RAM偺撪梕偼儐乕僓儕僙僢僩偐傜傑偨弶婜抣偵栠偡偙偲偑偱偒傑偣傫丅 RAM偺弶婜壔偺偨傔偵偼暿搑弶婜抣傪帩偮ROM偑昁梫偲側傝傑偡丅

丂巊偄曽偲偟偰偼丄ROM偵悇榑偝偣傞応崌偵偼mem偺弶婜抣傪愝掕偟丄 RAM偵悇榑偝偣傞応崌偼暿搑儐乕僓儕僙僢僩偵傛傝弶婜抣傪愝掕偡傞儘僕僢僋傪帩偭偰偍偔偙偲偑椙偝偦偆偱偡丅

丵

仴 SFL偵傛傞RAM巊梡忋偺拲堄

丂SFL偱mem愰尵傪梡偄偰RAM傪婰弎偟偨偲偡傞丅 偙偺偲偒丄堦売強偱偺write傗read側傜栤戣偲偼側傜側偄偑丄 暋悢売強偱write傗read偟偨応崌偵栤戣偲側傞丅 埲壓偺傛偆側婰弎傪偟偨応崌偵丄 僐儞僷僀儔偺RAM悇掕婡擻偵偆傑偔儅僢僠偣偢偵僐儞僷僀儖帪娫偑堎忢偵挿偐偭偨傝丄 BlockRAM偵儅僢僺儞僌偟偨偄偺偵Distributed RAM偵攝抲偝傟偨傝偟偰偟傑偆丅

丂傕偪傠傫暋悢売強偱偺write傗read偼丄僞僀儈儞僌揑偵廳側偭偰偄側偄偙偲偑慜採偩偑丅

丂僟儊側婰弎椺乮暋悢売強偱write傗read乯

mem ram[1024]<8>; ... ram[adrs1] := wdata1; ... ram[adrs2] := wdata2; ... rdata := ram[adrs3]; ... rdata := ram[adrs4];

丂偆傑偔RAM婰弎偲偟偰僐儞僷僀儔偵悇掕偝偣傞偵偼丄

堦売強偱偺write丄read偵傑偲傔傞昁梫偑偁傞丅

丂椙偄婰弎椺侾乮instrself偵傛傝write傗read傪傑偲傔偨乯

mem ram[1024]<8>;

sel ram_adrs<10>, wdata<8>;

instrself ram_write(ram_adrs, ram_wdata);

instrself ram_read(ram_adrs);

instruct ram_write par{

ram[adrs] := wdata;

}

instruct ram_read par{

rdata := ram[adrs];

}

...

ram_write(adrs1, wdata1);

...

ram_write(adrs2, wdata2);

...

ram_read(adrs3);

...

ram_read(adrs4);

丂暿搑RAM儌僕儏乕儖傪梡堄偟偰偍偄偰丄偙傟傪巊梡偡傞曽朄傕偁傞丅

偙偪傜偺傎偆偑妋幚偵BlockRAM傊儅僢僺儞僌偝傟傞丅

丂椙偄婰弎椺俀乮ram_8x1k.sfl傪梡堄偟偰偍偔乯

circuit ram_8x1k

{

input adrs<10>, din<8>;

output dout<8>;

instrin read(adrs);

instrin write(adrs, din);

mem cells[1024]<8>;

reg dout_reg<8>;

par{

dout = dout_reg;

}

instruct read dout_reg := cells[adrs];

instruct write cells[adrs] := din;

}

%i "ram_8x1k.h" ... ram_8x1k ram; ... ram.write(adrs1, wdata1); ... ram.write(adrs2, wdata2); ... ram.read(adrs3); ... ram.read(adrs4);

丵

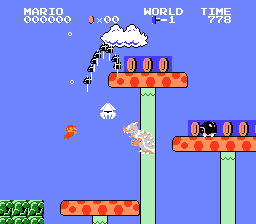

仴 惓偟偒悽奅偼峏抧偺忋偵 2012/12/07

悈拞僗僥乕僕偱僗僞乕僩捈屻偵僴儞儅乕傪搳偘偰偔傞僋僢僷(?)偝傫

丂儅儕僆偲僥僯僗偺僇乕僩儕僢僕傪巊梡偟偨桳柤側僶僌偑偁傝傑偡偹丅 懠偺僎乕儉偐傜揹尮傪愗傜偢偵僇乕僩儕僢僕傪嵎偟懼偊偨応崌丄僶僌傞帠偑偁傞丅 偙傟偼WRAM偵慜偺僎乕儉偺抣偑擖偭偨傑傑偱儅儕僆傪幚峴偡傞偨傔丅

丂幚婡偱偺WRAM偼SRAM側偺偱丄揹尮ON帪偺忬懺偼晄掕抣偲巚傢傟傞丅 儅儕僆偼偙傟傪専弌偟偰僛儘偱弶婜壔偡傞偦偆側丅 偨偩偟丄懠偺僎乕儉偐傜捈愙愗傝懼偊偨応崌偵偦傟偑専弌偝傟偢丄弶婜壔偝傟側偄応崌偑偁傞丅 懠偺偄偔偮偐偺僎乕儉偑僴儞僌偡傞偙偲傕WRAM弶婜壔偑偆傑偔幚峴偝傟側偄偙偲偑尨場偺傂偲偮偲峫偊傜傟傞丅 側偺偱丄WRAM偲丄偮偄偱偵VRAM傕嫮惂揑偵僛儘僼傿儖偡傞傛偆偵幚憰偟偨丅

丂帋偟偵塃偺夋憸偼丄僄儈儏偱

memset(wram, 0x00, 0x800);丂傪

for(i=0;i<0x800;i++) wram[i]=rand();丂偟偰弌偰偒偨僗僥乕僕丅

側偤偐僗僥乕僕抣傗揋僷僞乕儞抣偑弶婜壔偝傟偰偄側偄丅

丂傑偁偲偵偐偔僛儘僼傿儖偡傟偽栤戣側偄偱偟傚偆偲偄偆偙偲偱丄 SFL偱偺幚憰偼埲壓偺傛偆偵偟偨丅 僎乕儉ROM傪SD僇乕僪偐傜撉傒崬傫偱偄傞娫偵僛儘僼傿儖張棟傪幚峴偡傞丅

stage wram_init {

reg_wr mem_adrs<11>;

par{

wram.write(mem_adrs, 0x00);

vram.write(mem_adrs, 0x00);

mem_adrs++;

if(/&mem_adrs) finish;

}

}

丂偪側傒偵埨掕斉偺nslcore_20120527斉偱偼弌椡偝傟偨VerilogHDL偺RAM婰弎偑RAM悇榑偝傟偵偔偄婰弎偩偭偨偨傔丄 偆傑偔QuartusII偱儅僢僺儞僌偝傟偢丄傢偞傢偞弶婜壔婡擻傪帩偭偨儊儌儕傪嶌偭偨傝偟偨丅 nslcore_20120915斉埲崀偩偲惓忢偵儅僢僺儞僌偝傟傞傛偆偩丅