SNES on FPGA僗乕僼傽儈奐敪偺儊儌儔儞僟儉

丂僗乕僼傽儈偼梀傇偨傔偺傕偺偱丄奐敪偡傞偨傔偺傕偺偱偼偁傝傑偣傫丅

丂SFC丄偮傑傝僗乕僼傽儈傪FPGA偱帺嶌偟偨丄偲偄偆偍榖丅

丂僼傽儈僐儞偺帪戙丄摉帪偲偟偰偼崅偄惈擻偩偭偨偑偦傟埲忋偵幚尰偱偒側偐偭偨僋儕僄僀僞乕偨偪偺悽奅偑丄

僗乕僼傽儈偺帪戙偵側傝彮偟偢偮幚尰偟偮偮偁偭偨乮偦傟偼傕偆IC偑壩傪暚偐傫偑偛偲偔乯丅

僨僓僀僫乕丄僶僩儖僾儘僌儔儅丄僪僢僞乕丄僒僂儞僪僾儘僌儔儅乧

斵傜偺楌巎偺拞偱朼偑傟偰偒偨傕偺偼側傫偩偭偨偺偐丅

僗乕僼傽儈屳姺婡偺惢嶌丅偦傟偼僗乕僼傽儈偵偍偄偰嵟屻偺僎乕儉偲側傞丅

仴 奐敪娐嫬

僴乕僪僂僃傾婰弎尵岅

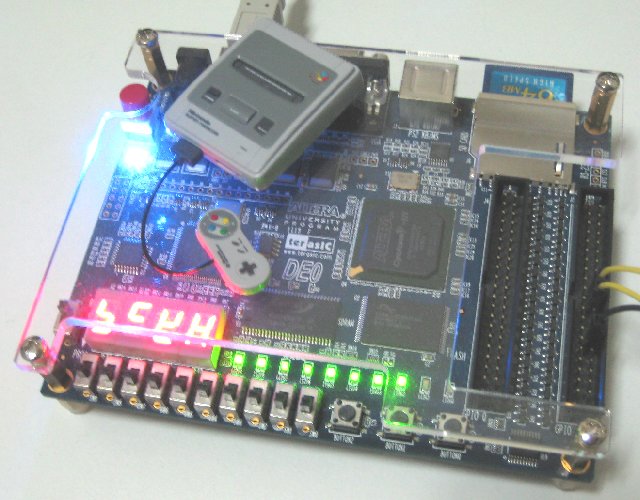

Terasic DE1 2005乣

Terasic DE2-115 2016乣

Terasic DE0-CV 2017乣

奐敪娐嫬

仴 摦嶌僨儌

丂SNES on FPGA (with original sound module)

丂Chrono Trigger demo. YouTube SNES on FPGA 僋儘僲僩儕僈乕僨儌

SPC Player on FPGA YouTube SNES SPC Player on FPGA feat. DE1

仴 偍偲側傝偝傫傪擿偄偰尒傟偽丄暥柧奐壔偺壒偑偡傞

丂2006擭枛丄岼偱偼PS3丄Xbox360丄Wii偲偄偭偨僗乕僷乕昤夋惈擻傪帩偮僐儞僔儏乕儅婡偑弌夞傝巒傔丄

僌儔僼傿僢僋傗儐乕僓僀儞僞僼僃乕僗偺恑壔偲傗傜偑彮偟尒偊偰偒傑偟偨丅

巹偺晹壆偵偼偦傟傜偺師悽戙婡偼偍傠偐僥儗價偝偊柍偄偗偳丅

偦傫側儀僞側僼傽儈僐儞偼偄傗偩両

丂偲偄偆怱偺嫨傃傪幚尰偟偨偺偑NES on FPGA 偱偁傝傑偡丅

僨傿僕僞儖夞楬偺暅廗偲FPGA偺楙廗傕偐偹偰偐傝偐傝幚憰偟偨傢偗偱偡偑丄

偙偺偲偒偼乽傢偁FPGA偭偰曋棙側傫偩偹偉乿掱搙偵偟偐峫偊偰偄側偐偭偨偺偑偄傑傗

FPGA偵嬯偟傔傜傟傞棫応偵乧僐儞僾儔僀傾儞僗偭偰僫儞僟乕両

NEXT GENERATION

丂梡岅偺曗懌

丂SNES on FPGA偺奐敪娐嫬偲偟偰偼丄 奐敪僾儘僙僗傪側偧傝側偑傜尒偰偄偒傑偡丅

儀乕僗偼NES on FPGA偺奐敪僾儘僙僗偱偡丅

偨偩偟婯柾偑戝偒偔側傞偨傔偦傟側傝偵岠棪揑側専徹曽朄傪摫擖偡傞昁梫偑偁傝傑偡丅

丒巇條傪攃埇偟傠両

丒僄儈儏儗乕僞嶌惉

丒僴乕僪僂僄傾婰弎撈帺奼挘偟偨SFL+ 偼傛傝戝婯柾側SNES偺奐敪偵栶偵棫偪傑偟偨丅

丒僔儈儏儗乕僔儑儞

丒SFL偐傜VerilogHDL傊偺曄姺

丒偦偺FPGA儃乕僪偍偄偟偄偺丠

丒晄嬶崌傪尒偮偗弌偣両

丒偼偨偟偰寢壥偼乧

丒嵞尰惈傪忋偘傞両

丂偙偆偟偰SNES on FPGA偼姰惉偵嬤偯偄偰備偔偺偱偟偨丅

仴 奐敪棜楌

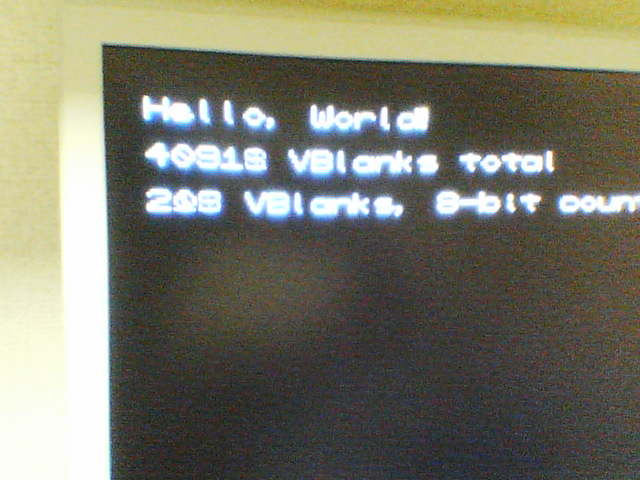

FPGA偵偰Hello World!傪昞帵 丅仺

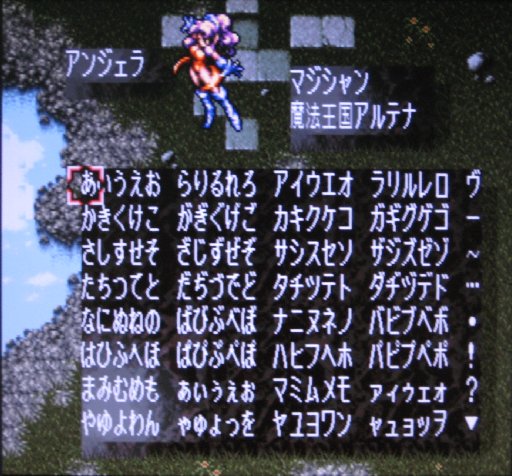

傢偵傢偵嬩妝晹

偺奺僜僼僩偵偮偄偰幚峴偟側偑傜偺幚憰丅

乽儘僢僋儅儞倃乿偵偮偄偰偺幚憰丄

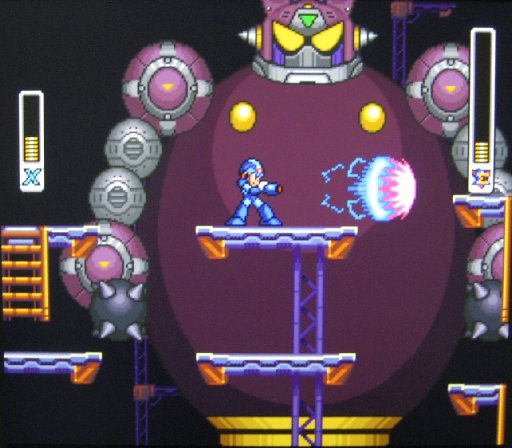

APU傊偺傾僋僙僗偑擖偭偰偒偰偐傜柦椷偺僩儗乕僗偑僄儈儏偲崌傢側偔側偭偨偨傔丄

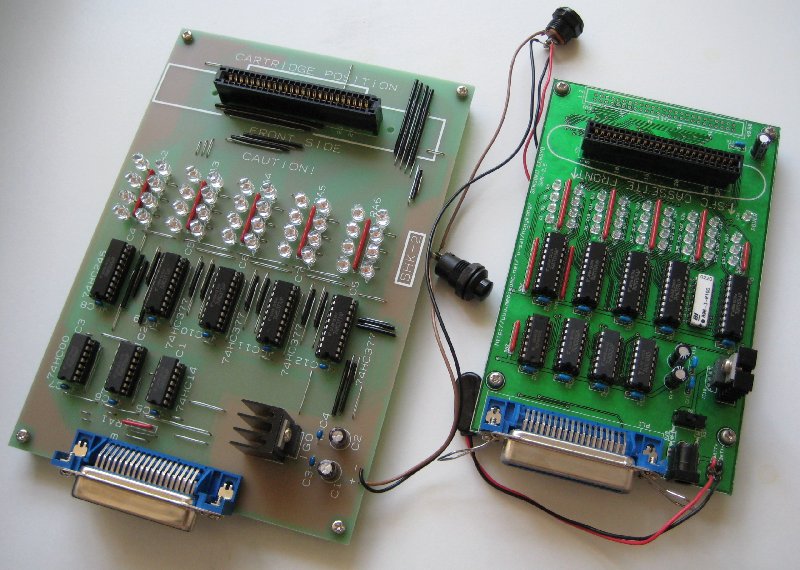

幚婡偺APU儌僕儏乕儖傪愙懕偡傞丅

偦傟偱傕僐傾APU偲曄傢傜側偄偺偱偲傝偁偊偢幚憰偟偨偲偙傠幚峴偱偒偨丅

FPGA偵偰乽儘僢僋儅儞倃乿偑僾儗僀偱偒偨 丅

乮It is playable MegaManX on FPGA乯仺

MiSTer僔僗僥儉 偵壖堏怉丅

偣偭偐偔側偺偱HDMI偐傜塮憸弌椡偱偒傞傛偆偵偟偨偄丅

spcmake_byFF4

spcmake_byFF5

spcmake_byFF6

婃挘偭偰帹僐僺偟偨傕偺伀

Tang Nano 20K 偵堏怉丅

偨偩偟丄LUT偑懌傝偢僒僂儞僪DSP傪彍奜偟丄

僒僂儞僪儊儌儕偵偮偄偰偼16kByte偺傒BlockSRAM偱幚憰丅

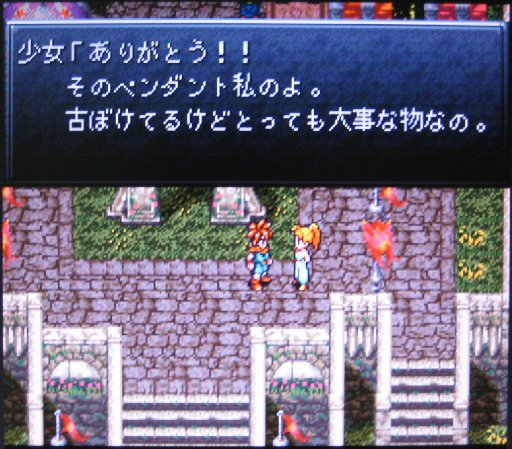

乽僋儘僲僩儕僈乕乿乽僶僴儉乕僩儔僌乕儞乿偺OP僨儌傪僷僗丅

巊梡FPGA儃乕僪

巊梡FPGA儃乕僪

2007/02/10

乽偵傘乕傠偱僼傽僕乕側僔儏乕僥傿儞僌乿偵偰

張棟懍搙偑嬌抂偵棊偪偰偄偨偺偼SBC偺fc偑斀懳偩偭偨偨傔丅

墘嶼柦椷僠僃僢僋傪幚巤丅

2007/02/10

乽偵傘乕傠偱僼傽僕乕側僔儏乕僥傿儞僌乿偵偰

張棟懍搙偑嬌抂偵棊偪偰偄偨偺偼SBC偺fc偑斀懳偩偭偨偨傔丅

墘嶼柦椷僠僃僢僋傪幚巤丅

SpritePriorityRotation傪廋惓丅嵍忋偺儅儕僆偑昞帵偝傟偨丅仺

SpritePriorityRotation傪廋惓丅嵍忋偺儅儕僆偑昞帵偝傟偨丅仺

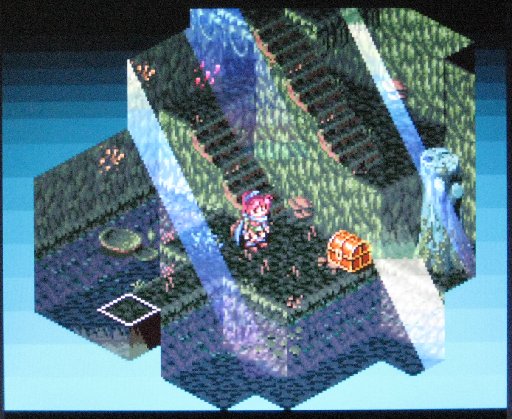

BG mode7偺ExtBG儌乕僪傪幚憰丅

乽偒偖傞傒戝朻尟乿偺儚乕儖僪儅僢僾偺怓偑偒傟偄偵昞帵偝傟偨丅仺

BG mode7偺ExtBG儌乕僪傪幚憰丅

乽偒偖傞傒戝朻尟乿偺儚乕儖僪儅僢僾偺怓偑偒傟偄偵昞帵偝傟偨丅仺

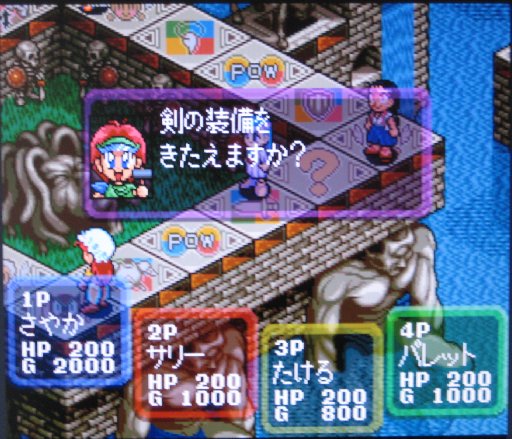

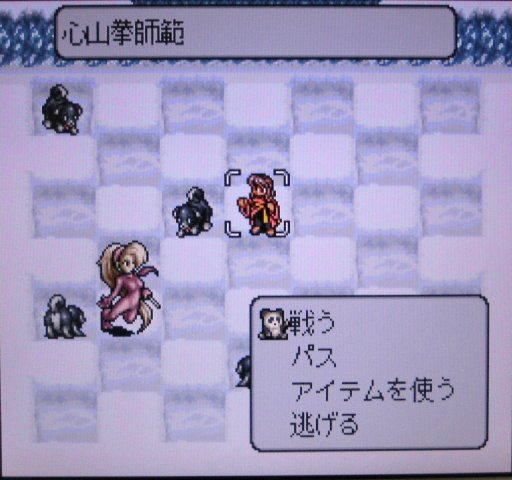

僗僾儔僀僩僼僃僢僠嵟戝34屄傑偱傪僒億乕僩丅

乽FF5乿偺僶僢僣偑昞帵偝傟偨丅乮32屄傑偱惂尷偟偰偄傞偲僶僢僣偑昞帵偝傟側偄乯仺

僗僾儔僀僩僼僃僢僠嵟戝34屄傑偱傪僒億乕僩丅

乽FF5乿偺僶僢僣偑昞帵偝傟偨丅乮32屄傑偱惂尷偟偰偄傞偲僶僢僣偑昞帵偝傟側偄乯仺

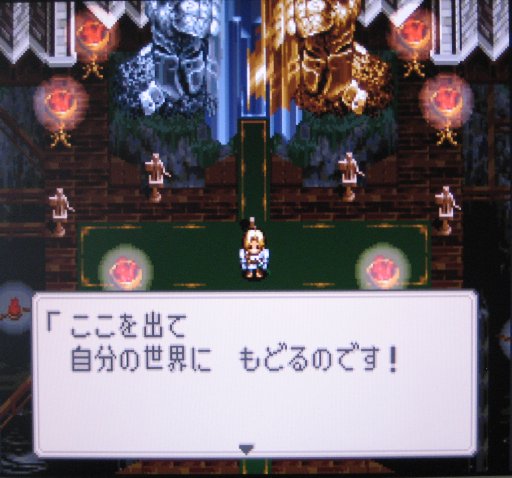

BG mode5,6偺墶夝憸搙512僪僢僩傪弶婜幚憰丅

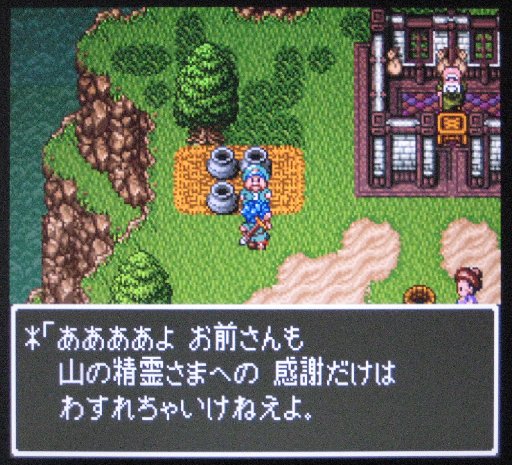

乽惞寱揱愢俁乿乽偲偒傔偒儊儌儕傾儖乿側偳BGmode5傪巊梡偟偰偄傞僎乕儉偺暥帤偑撉傔傞傛偆偵側偭偨仺

BG mode5,6偺墶夝憸搙512僪僢僩傪弶婜幚憰丅

乽惞寱揱愢俁乿乽偲偒傔偒儊儌儕傾儖乿側偳BGmode5傪巊梡偟偰偄傞僎乕儉偺暥帤偑撉傔傞傛偆偵側偭偨仺

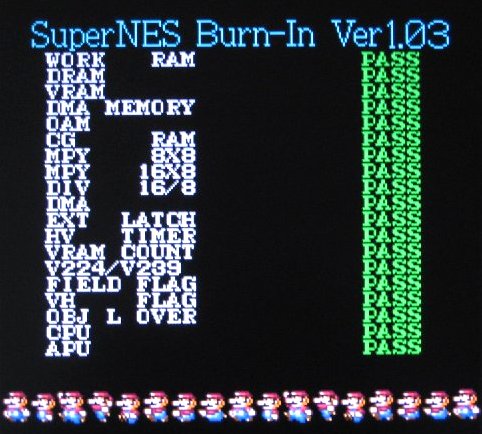

VBlank偺奐巒儔僀儞傪224偐傜225偵廋惓偟偰丄Burn-In僥僗僩偺V224/V239傪PASS偟偨丅

VBlank偺奐巒儔僀儞傪224偐傜225偵廋惓偟偰丄Burn-In僥僗僩偺V224/V239傪PASS偟偨丅

2019/01/08

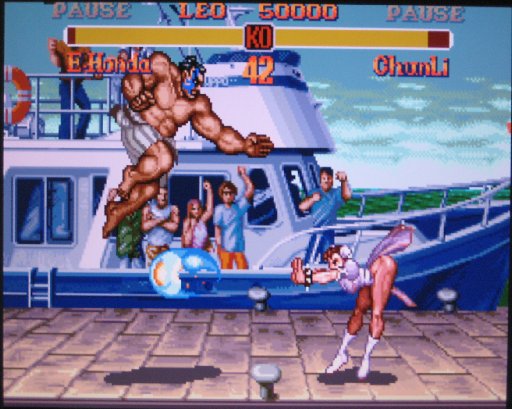

Cx4僠僢僾偺弶婜幚憰偱僗僾儔僀僩偑昞帵偝傟

乽儘僢僋儅儞倃俀乿乽儘僢僋儅儞倃俁乿偑僾儗僀偱偒傞傛偆偵側偭偨丅

2019/01/08

Cx4僠僢僾偺弶婜幚憰偱僗僾儔僀僩偑昞帵偝傟

乽儘僢僋儅儞倃俀乿乽儘僢僋儅儞倃俁乿偑僾儗僀偱偒傞傛偆偵側偭偨丅

丒

丒