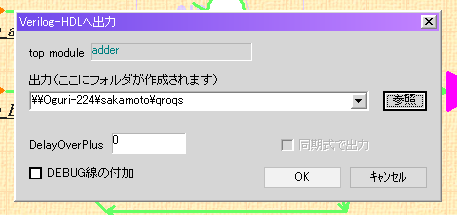

| Verilog-HDLファイルの出力とSynopsysによる論理合成 |

VerilogライブラリとしてROHM社製、0.35μmテクノロジを使用しています。

出力先のディレクトリに、[top module]名でフォルダが作成されます。

| Makefile | 言わずもがな、make、g++、コマンド必須。 | |

|---|---|---|

| add.dc | top module論理合成用dc_shellスクリプト | |

| add.v | top module | |

| add_sim.v | シミュレーションmodule | |

| arbiter.v | アービタmodule,必要なくてもとりあえず。 | |

| delay.data | 遅延情報 | |

| delay.v | 遅延module群。トランジション関数の遅延は入っていません | |

| delayadd.cpp | BUFによる遅延moduleを合成するためのコード、make dc時にコンパイルされる。 | |

| kemmakixuhzi.v | シミュレーションで使用されるウージとケムマキmodule。論理合成は行われない。 | |

| muller_c.v | mullerのC素子module。リセット時に0を出力するもの(muller_c_r)と1を出力するもの(muller_c_s) | |

| pipe.v | 制御線module群。入出力数で区分 | |

| pjoint.v | 選択分岐や競合合流部分の接続module群 | |

| trafunc.v | トランジション関数module群。機能記述なので遅延なし | |

| transition.v | トランジションmodule群 | |

| udata*.txt | ウージデータ。*には番号が入る |

シミュレーションは

| % make |

により行います。

ライブラリが見つからないといわれる場合は、Makefileを編集してください

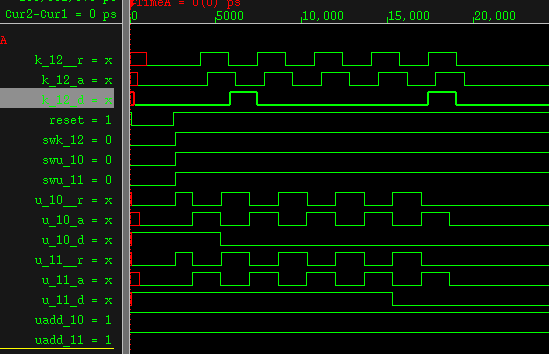

終わったらsignalscanで波形を確認しましょう。

k_12_dが出力されるデータです。QROQS上でもIDは12でした。

データは、k_12_aの立ち上がりエッジの時間の時に有効になるので、

00001と有効データが出力されていることが分かります。

また、ファイルkdata12.txtを見ることでも出力データを確認できます。

| % make dc |

により、多少時間がかかりますが、合成を行います。詳細は、

1.遅延付加スクリプトのコンパイル 2.トランジション関数の論理合成 3.レポートファイルより遅延時間を取得 4.遅延モジュールの生成 5.トランジション関数、遅延モジュールを含めたtop moduleの論理合成となっています。

合成後、ここまでで新たに出力されるファイルとして主なものは、

| add.rep | top module合成結果レポートです。面積はここから取得してください | |

|---|---|---|

| add.vnet | 論理合成をおこなったtop module | |

| delay.vnet | トランジション関数の遅延を加算し、遅延を偶数個のINVで構成した遅延module | |

| delayadd | 遅延module生成用コマンド | |

| kdata*.txt | ケムマキに出力されるデータ。*にはIDが入る. |

| % make sim |

により、シミュレーションを行います。

結果は先ほどと同じように、波形及びデータ出力ファイルで確認して下さい。