| NES on FPGA | 2005/01/09 |

カートリッジ

ゲームプログラムを格納したカートリッジには下記のものが含まれます。

- ・PRG-ROM(Program ROM)

- プログラムが格納されています。

- ・CHR-ROM(Character ROM)

- キャラクタやバックグラウンドのパターンが含まれます。

- ・MMC(Multi Memory Controller)

- PRG-ROM以上のROMが搭載されていたり、 NESに内蔵されたRAM以上のメモリが必要だったりする場合に追加され、 カートリッジ内のバンク切り替えなどを行います。

- ・拡張RAM

- カートリッジによってはRAMを搭載しています。

- ・拡張オーディオチップ

- カートリッジによっては拡張音源を搭載しています。

_

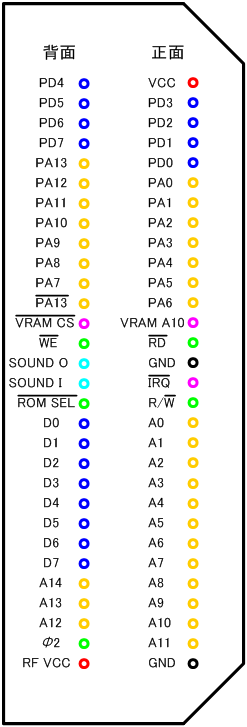

▼ コネクタピン配置

ファミコン本体のコネクタを上から見た図になります。

北米版NESのコネクタとはピン数やピン配置等が異なります。

|

●+5V ●GND ●データ双方向 ●アドレス出力 ●制御出力 ●制御入力 ●サウンド

|

VCC、RFVCC:

共に5V電源。

PD0〜7: CHA-ROMからのパターンデータ入力。もしくは拡張RAMへのデータ出力。 PA0〜13、/PA13: CHA-ROMへのアドレス出力。 /VRAM_CS: VRAMのCSピンへの入力。負論理によりVRAMが選択される。(CS:Chip Select) VRAM_A10: VRAMのA10ピンへの入力。 /WE、/RD: CHR-ROMもしくは拡張RAMへの制御出力。

GND:グラウンド。 SOUND I、O: APUで生成されたサウンドはInから出力され、 拡張音源がある場合は合成され、Outから入力される。 /IRQ: IRQ割り込み信号が入力され、 負論理によってIRQ割り込みが検出される。 IRQ割り込みを使用しない カートリッジではこのラインはどこにも接続されていない。 本体内部では、このラインはプルアップされている。 /ROM_SEL: 負論理の出力によってカートリッジ内PRG-ROMが選択される。 R/W: PRG-ROM(もしくは拡張RAM)への出力。

D0〜7: PRG-ROMからのプログラム入力。もしくは拡張RAMへのデータ出力。 A0〜14: PRG-ROMへのアドレス出力。 φ2: カートリッジへの同期出力。 この信号は、CPUへ入力されるクロック信号から数十nsほど遅延がついている。

|