| NES on FPGA | 2014/08/10 |

dev PPU

|

丂PPU偵娭偡傞僴乕僪僂僃傾婑傝偺徻嵶側帒椏偑尒摉偨傜側偐偭偨偨傔丄 堦斣帪娫偑偐偐偭偰偟傑偭偨偲偙傠偱偡丅 BG偲SPR偑堦柺偢偮偩偗側偺偱丄偦傟偧傟幚憰傪恑傔偰偄偒傑偟偨丅 | ! | 側傔傜偐側僗僋儘乕儖傪丄夛応偵偰偛妋擣壓偝偄丅 |

丵

仴 Ver.1 僜僼僩僄儈儏偐傜僴乕僪僔儈儏傊

丂僜僼僩僄儈儏偱幚憰偟偨傕偺傪僴乕僪僂僄傾婰弎偵側偍偡嶌嬈偼丄

摉慠側偑傜僋儘僢僋僞僀儈儞僌偲偺愴偄偵偮偒傑偡丅

偲傝偁偊偢僗僾儔僀僩偼抲偄偲偄偰丄

攚宨偺僨乕僞僼僃僢僠偲昤夋僞僀儈儞僌傪愝寁偟傑偟偨丅

弌椡偼奺僺僋僙儖偵懳偟偰1Byte偺僷儗僢僩僨乕僞偲側傝傑偡丅

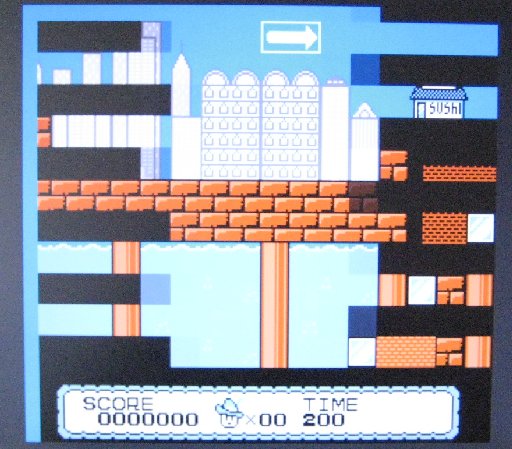

僔儈儏儗乕僔儑儞偱惗惉偟偨BG夋柺

丂昤夋僥僗僩偱儅儕僆偺僞僀僩儖夋柺傪昤夋偟傛偆偲偟偰偄傑偟偨偑丄 偙偙偱拲堄偡傋偒偼僗僾儔僀僩僛儘僸僢僩偑巊傢傟偰偄傞偲偄偆偙偲偱偡丅 僛儘僸僢僩偺僞僀儈儞僌偱僗僋儘乕儖偝傟偰偄傞傛偆側偺偱丄 壖憐揑偵30斣栚偺僗僉儍儞儔僀儞晅嬤偱僗僾儔僀僩僛儘僸僢僩僼儔僌傪僙僢僩偟偰傗傞昁梫偑偁傝傑偡丅

丂PARTHENON偱僔儈儏儗乕僔儑儞傪峴偄丄 揻偒弌偝傟偨僨乕僞傪張棟偟偰256x240偺PNG夋憸傪惗惉偟傑偟偨丅 攚宨偼丄33僼儗乕儉栚偵傛偆傗偔昤夋偝傟傞偨傔丄 Pentium4(2.4GHz)儅僔儞偱偺僔儈儏儗乕僔儑儞偱20暘傎偳偐偐傝傑偟偨(偆傊偉)丅

丵

仴 Ver.2 僴乕僪僔儈儏偐傜僴乕僪傊

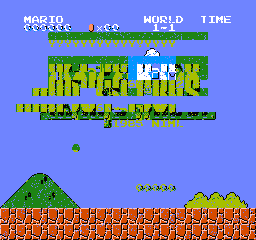

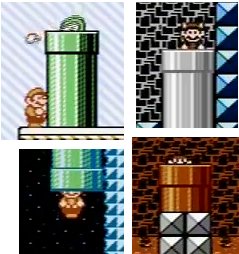

FPGA偱BG夋柺傪昞帵偟傛偆偲偟偨寢壥乮僀儊乕僕乯

丂僔儈儏儗乕僔儑儞偱20暘偐偐偭偰偪傖傗偭偲傟傫偺偱FPGA傊丅 昡壙儃乕僪傕擖庤偱偒偨偺偱丄僇乕僩儕僢僕傪僐僱僋僩偟偰僐儞僼傿僌丅

丂傑偨VGA傊偺弌椡傊懳墳偡傞偨傔偵丄PPU偺弌椡傪侾儔僀儞暘偨傔傞僶僢僼傽傪偐傑偟偨丅

丂昤夋偼傑偁丄僇乕僩儕僢僕偺崁偵傕偁傝傑偡傛偆偵丄 CHR-ROM偐傜Read偟偰傕攝慄偑挿偔僲僀僘偑懡偔偰晄埨掕丅 僞僀僩儖偺昤夋傑偱偼妋擣偱偒傑偡偑丄僾儘僌儔儉掆巭丅 椢怓偺僞僀僩儖側傫偰偳偙偺儂儔乕塮夋偐丅 僇乕僩儕僢僕僐僱僋僞偺夵椙傊丅

丵

仴 Ver.3 儅仜僆偑乧儅儕仜偑棫偭偨傢両

丂儅儕僆偑昤夋偝傟側偄儅儕僆側傫偰儅儕僆偠傖偹偊偺偱丄 偡偖偵FPGA傊幚憰偡傋偒側偺偱偡偑壞媥傒側偺偱幚壠傊丅 側傫偱幚壠偱僗僾儔僀僩偺愝寁丠壠懓偺帇慄偑側傑偁偨偨偐偄乧丅

丂僗僾儔僀僩偺扵嶕偲僷僞乕儞僼僃僢僠偺僞僀儈儞僌偼攚宨偺昤夋偺崌娫偵峴傢傟偰偄傞偨傔丄 攚宨偺昤夋僞僀儈儞僌偺尒捈偟偼昁梫偁傝傑偣傫偱偟偨丅 偙傟偼憐掕偳偍傝丅

丂師偺僗僉儍儞儔僀儞偱昤夋偝傟傞傋偒僗僾儔僀僩偺扵嶕偺偨傔偵丄 僗僾儔僀僩僥儞億儔儕儗僕僗僞傪8僗僾儔僀僩暘梡堄偡傞昁梫偑偁傝傑偡丅 儗僕僗僞傪堦搙偵偙傫側偵戝検偵巊偄姷傟偰側偄偺偱懡彮屗榝偄傑偟偨偑丄 偺偪偺SFL+偱偼戝検偺儗僕僗僞傪梕堈偵埖偊傞婰弎傪摫擖偟偰儔僋僠儞偱偡丅

|

傛偆傗偔僗僾儔僀僩偑昞帵偱偒偨 |

BG偲僗僾儔僀僩傪慻傒崌傢偣偰姰惉両 |

丂偝傜偵扵嶕僗僥乕僕傪婰弎丅 奺僗僾儔僀僩偵娭偟偰4僋儘僢僋亊64僗僾儔僀僩偱256亄偦偺懠亖258僋儘僢僋傪梫偟傑偡偑丄 攚宨昤夋僋儘僢僋偵廂傑傝傑偟偨丅 昤夋斖埻奜偺僗僾儔僀僩傪柍帇偡傞傛偆偵偡傟偽16僗僾儔僀僩傕壜擻偱偡偐両丠

丂僗僾儔僀僩偺僷僞乕儞僨乕僞偺偨傔偵僗僾儔僀僩僶僢僼傽儗僕僗僞傪丄 偦傟偧傟8僗僾儔僀僩暘梡堄偡傞昁梫偑偁傝傑偡丅 攚宨昤夋偑廔傢偭偰丄悈暯摨婜傑偱偺娫偵8僗僾儔僀僩暘偺僨乕僞傪僼僃僢僠偡傞僗僥乕僕傪捛壛丅 奺僗僾儔僀僩偱6僋儘僢僋亊8僗僾儔僀僩偱48亄偦偺懠亖50僋儘僢僋偱廂傑傝傑偟偨丅 偙偺僷僞乕儞僨乕僞僼僃僢僠偑偁傞偐傜16僗僾儔僀僩偼擄偟偄傛偆偱偡丅 乮幚偼16僗僾儔僀僩傕壜擻側傫偱偡偑偦傟偼傑偨偄偢傟乯

丂旕椡側僲乕僩僷僜僐儞偱偺僔儈儏儗乕僔儑儞偼帪娫偑偐偐傝傑偟偨偑丄 34僼儗乕儉栚偵傛偆傗偔儅儕僆偑尰傟傑偟偨丅 廻戣廔傢傝丅

丂幚壠偐傜栠傝丄FPGA傊偺幚憰偱傕昤夋傪妋擣丅 怣崋傕埨掕偟丄傛偆傗偔僨儌偱儅儕僆偑憱偭偰傑偡丅 崌惉寢壥丄懍搙嵟揔壔

Total equivalent gate count for design: 46,810偙傟偐傜RAM偺僎乕僩悢16,390亊2傪堷偄偰丄亖14,030僎乕僩丅偳偆側傫偩傠丅 柺愊嵟揔壔偱1,000僎乕僩尭傜偣傞傫偩偗偳側丅 僀儞僋儕儊儞僞儖僐儞僷僀儖挷傋側偄偲乧

丂僇儔乕偼丄奺僪僢僩偵懳偟偰6價僢僩偺僺僋僙儖僨乕僞傪弌椡偟傑偟偨丅 VGA弌椡偵偼丄壓埵4價僢僩偱RGB奺3價僢僩偐傜惉傞怓傪慖戰偟丄 忋埵2價僢僩傪柧搙偲偟偰壛嶼偟偨寢壥傪弌椡偟傑偟偨丅 傛偔尒傞偲丄慡懱揑偵敄偄傛偆側婥偑偟傑偡丅

|  |

| 僐僀儞僇僂儞僞 | 丂朸仜儕僆 |

丂儅儕僆偱梀傫偱偰婥晅偔丅

儅儕僆偑僐僀儞僇僂儞僞乮攚宨乯偵廳側傞偲丄

攚宨傛傝傕桪愭搙偑掅偄偼偢偺僺僋僙儖乮僗僾儔僀僩僛儘乯偑昤夋偝傟偰偄傞丅

偙傟偼丄僗僾儔僀僩偲攚宨丄媦傃僗僾儔僀僩摨巑偺桪愭弴埵偱柕弬偟偰偄傞傕偺傪昤夋偟偰偄傞偐傜丅

幚婡偱傕偙偺尰徾偑婲偒傞偙偲傪妋擣偟偨偺偱丄偁偙傟偱偄偄偺偐丄偲丅

丵

仴 Ver.4 岲偒側偔偣偵

丂嵐梾欀幹側偳偱巊梡偝傟傞丄 IRQ妱傝崬傒偵傛傞儔僗僞僗僋儘乕儖偵懳墳偡傞偨傔丄 僗僋儘乕儖儗僕僗僞偺彂偒崬傒売強傪曄峏丅 攚宨偲偄偭偟傚偵僗僋儘乕儖偟偰偄偨揰悢昞帵偑屌掕偝傟傞傛偆偵側傝傑偟偨丅

丂僀儘僈丄僗僐僔僠僈僀儅僗僇丠偲偺偛巜揈傪捀偄偨傢偗偱偡偑丄

敪怓偼僥儗價偺愝掕側偳偵傛偭偰條乆偱偁傞傕偺偺丄

僷儗僢僩傪儚僀儎乕僪儘僕僢僋偱傗傞偺偼怓曄峏傕帺桼偵偱偒側偄偺偱丄

64怓偺RGB僇儔乕傪ROM偲偟偰帩偮偙偲偵偟傑偟偨丅

丂僀儘僈丄僗僐僔僠僈僀儅僗僇丠偲偺偛巜揈傪捀偄偨傢偗偱偡偑丄

敪怓偼僥儗價偺愝掕側偳偵傛偭偰條乆偱偁傞傕偺偺丄

僷儗僢僩傪儚僀儎乕僪儘僕僢僋偱傗傞偺偼怓曄峏傕帺桼偵偱偒側偄偺偱丄

64怓偺RGB僇儔乕傪ROM偲偟偰帩偮偙偲偵偟傑偟偨丅

丂嵍偑12怓亄柧搙丄塃偑64怓丅

僞僟働乕僞僀偺僇儊儔偼偩傔偩側丅

64怓偺曽偑儊儕僴儕偑棙偄偰傑偡側丅

偱傕偙傟偼岲傒偺栤戣偩傛側偁丅

乮12怓亄柧搙偱傗傞偺偑幚婡偵嬤偄傜偟偄乯

丵

仴 僫乕僔儍丒僕儀儕巵傊偺挧愴丂2008/10/14

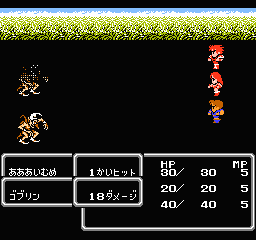

FF2丗揋傪搢偟偨偲偒偺僄僼僃僋僩

丂FF2偵偍偄偰丄揋偲偺憳嬾帪傗揋傪搢偟偨帪偺僄僼僃僋僩帪偵丄 夋柺偑偪傜偮偔栤戣偑敪惗偟偨丅

丂捠忢VBlank廔椆慜偵僗僋儘乕儖抣傪愝掕偡傞偑丄 PPU傊偺write儘僌傪尒偰傒傞偲丄

丂1. 僗僾儔僀僩僸僢僩懸偪

丂2. NMI桳岠

丂3. 僗僋儘乕儖抣愝掕

丂4. VBlank奐巒

丂5. 僗僾儔僀僩僨乕僞揮憲

丂6. VRAM僨乕僞揮憲

丂7. 僗僾儔僀僩僸僢僩僋儕傾懸偪

丂8. VBlank廔椆

丂9. 僗僋儘乕儖抣愝掕

丂1. 僗僾儔僀僩僸僢僩懸偪乮嵟弶偵栠傞乯

8.偺VBlank廔椆慜偱偼側偔丄幚偼7.偺僗僾儔僀僩僸僢僩僋儕傾傪僩儕僈偲偟偰僗僋儘乕儖抣傪write偟偰偄偨傛偆偩丅

丂PPU偺HDL傪尒偰傒傞偲丄僗僾儔僀僩僸僢僩僋儕傾偲丄僗僋儘乕儖抣偺斀塮傪摨偠僞僀儈儞僌偱峴偭偰偄偨丅

偙偺偨傔丄惓偟偔僗僋儘乕儖抣偑斀塮偝傟側偄偱丄偪傜偮偒偑敪惗偟偰偄偨柾條丅

丂僗僾儔僀僩僸僢僩僋儕傾偺師偺儔僀儞偱丄僗僋儘乕儖抣傪斀塮偡傞傛偆偵偟偨偲偙傠偪傜偮偒偑側偔側偭偨丅

丵

仴 僗僾儔僀僩尷奅撍攋丠

丂1儔僀儞偵昞帵偱偒傞僗僾儔僀僩偼嵟戝8屄傑偱丄偵偮偄偰丅

丂僪儔僋僄側偳偱嵟戝4恖僷乕僥傿偲側偭偰偄傞棟桼偑丄 1儔僀儞偵昞帵偱偒傞僗僾儔僀僩偑8屄傑偱偲偄偆PPU偺巇條偐傜偒偨傕偺偱偁傞偲偄偆偙偲偼桳柤側榖丅 偨偩偟僜僼僩偵傛偭偰偼丄僼儗乕儉枅偵僗僾儔僀僩偺桪愭弴埵傪曄偊丄 揰柵偝偣傞偙偲偱媅帡揑偵9屄埲忋偺僗僾儔僀僩傪昞帵偡傞偲偄偆僥僋僯僢僋傪巊偭偰偄傞丅

丂傕偪傠傫丄PPU傪FPGA偱幚憰偡傞偵偁偨偭偰丄 婯掕僋儘僢僋偱偺僷僞乕儞僼僃僢僠傪柍帇偡傟偽摨帪偵9屄埲忋偺僗僾儔僀僩傪昞帵偝偣傞偙偲偼壜擻 乮50MHz偵偰扵嶕576屄丄僷僞乕儞僼僃僢僠191屄丄偲偄偆婘忋寁嶼乯丅

丂偨偩偟丄僪儔僋僄嘩側偳偱偼丄8屄傑偱偟偐昞帵偱偒側偄偲偄偆偙偲傪棙梡偟偰丄 僗僋儘乕儖帪偵堄恾揑偵僗僾儔僀僩傪旕昞帵偵偡傞墘弌偑巊傢傟偰偄傞丅 傑偨丄偪傜偮偒偑偁傞偺傕庯偑偁傞偲偄偆偙偲傕偁傝丄 僗僾儔僀僩幚憰偼8屄傑偱偵偲偳傔偰偍偔丅

丵

仴 僗僾儔僀僩僆乕僶乕僼儔僌偭偰巊偊偹偉

丂僗僾儔僀僩偑8屄埲忋昞帵偝傟傞応崌丄 PPU儗僕僗僞$2002偺價僢僩5偺僼儔僌偑棫偮偲偄偆巇條偑偁傞偑丄 偙偺偁偨傝丄8屄埲忋側偺偐9屄埲忋側偺偐帒椏偵傛偭偰僶儔僶儔丅 8屄偼昞帵偱偒傞偐傜僼儔僌傪棫偰偰抦傜偣傞昁梫偼側偄傫偠傖側偄偐偲巚偆丅 専嶕寢壥偑9屄埲忋偺応崌偵僼儔僌傪棫偰傞偙偲偱丄 揰柵偝偣傞側傝偟偰張棟偡傞偙偲偑揔愗偠傖側偄偐丠偲巚偭偨丅

丂崱偺偲偙傠夝愅寢壥偲偟偰偼9屄埲忋偱僼儔僌偑棫偮偲偄偆偙偲傜偟偄偑丄 僗僾儔僀僩儊儌儕偺撪梕偵傛偭偰偼8屄偱傕僼儔僌偑棫偮応崌偑偁傞傜偟偄丅 偍偦傜偔昞帵僗僾儔僀僩偺扵嶕儘僕僢僋傪嶍尭偟偨偙偲偵傛傞巇條奜偺摦嶌傒偨偄偩偑丄 偙偺偁偨傝偼幚憰偡傞昁梫惈傪姶偠側偄丅 扨弮偵9屄埲忋偱僼儔僌傪棫偨偣傞幚憰偲偟偰偄傞丅

丂偦傕偦傕偙偺僼儔僌傪尒偰偄傞僜僼僩偼偁傞偺偐丠 僪儔僋僄嘩偱帋偟偰傒偨偑丄 偙偺僼儔僌傪棫偰偨傝棫偰側偐偭偨傝偟偰傕昁偢5僉儍儔偱揰柵偡傞偙偲偐傜僼儔僌偼尒偰偄側偄傛偆偩丅

DQ4丗僗僾儔僀僩儘乕僥乕僔儑儞

丂2024/03/22捛婰丗

僪儔僋僄IV儊僀儞僾儘僌儔儅乕偺撪摗姲巵偵傛傞偲丄

僗僾儔僀僩僆乕僶乕僼儔僌偼尒偢偵僗僾儔僀僩儘乕僥乕僔儑儞偟偰偄傞偲偺偙偲丅

偦傟傕昞帵偡傞暘偩偗偺儘乕僥乕僔儑儞偱偼側偔丄

憖嶌僉儍儔埲奜偺(64-4)/4=15僉儍儔暘傪忢偵慡偰儘乕僥乕僔儑儞偟偰偄傞丅

偙傟偵傛傝忦審暘偗偡傞偙偲側偔張棟帪娫傕堦掕偵側傞儊儕僢僩偑偁傞丅

丂岼偺僄儈儏偱偼8屄埲忋偱僼儔僌偑棫偮幚憰偲側偭偰偄傞傕偺傕偁傞偑丄 偙傟偼扵嶕懍搙傪岦忋偝偣傞偨傔偺張抲偩偲巚傢傟傞丅 寢嬊丄栶偵棫偪偦偆傕側偄僼儔僌偲偄偆寢榑偲側偭偨丅

丵

仴 抪偢偐偟偄偐傜尒側偄偱乧丂2011/08/08

僼傽僀傾乕僄儉僽儗儉丗嵍忋偺偛傒

丂僼傽僀傾乕僄儉僽儗儉偱嵍忋偵偛傒偑弌傞丅 暿偵嵍8僪僢僩傪昞帵偟側偄僼儔僌傕愝掕偝傟偰偄側偄偺偱偙傟偼惓忢偺傛偆偩丅

丂偙傟偼丄捠忢忋8儔僀儞偼昞帵偝傟偰偄側偄僼傽儈僐儞偺巇條偵傛傝塀傟偰偄傞晹暘偱偁偭偰丄 TV側偳偱僾儗僀偡傞暘偵偼栤戣偵偼側傜側偄丅 僄儈儏偱傕忋8儔僀儞傪昞帵偟側偄傕偺偱偁傟偽僑儈偼塀傟傞丅 偑丄慡儔僀儞傪昞帵偡傞愝掕偵偡傞偲弌偰偔傞丅

丂僼傽儈僐儞偺巇條忋丄嵍8僪僢僩偲忋8儔僀儞偵娭偟偰偼丄 僗僋儘乕儖側偳偺嵺偵僞僀儖斣崋側偳偑嫬奅偺忋偵側傝丄 怓偑曄傢偭偨傝堎側傞僷僞乕儞偑昞帵偝傟偨傝丄 僗僾儔僀僩偑愗傟偨傝偟傗偡偄丅 偦偆偄偭偨埆尒傪塀偡偨傔偺PPU儗僕僗僞$2001偺儅僗僋僼儔僌偑偁傞丅 偱傕愝掕偝傟偰側偄偙偲傕懡偄傫偩傛偹丅

丵

仴 僗僾儔僀僩僑乕僗僩偺夦丂2012/12/23

儈僱儖僶僩儞僒乕僈丗僑儈偑乧

丂側傫偩偐僑儈偑弌傞丅 儈僱儖僶僩儞僒乕僈偱僜僼僩儕僙僢僩捈屻偺僞僀僩儖夋柺傗丄 儖乕僩16僞乕儃偱偺夋柺愗傝懼偊帪偵弌傞丅 傛偔尒傞偲僗僾儔僀僩偑偁偭偨埵抲偵弌傞傛偆偱丄 僗僾儔僀僩RAM傊偺傾僋僙僗偑夦偟偄偲偁偨傝傪晅偗偨丅

丂僄儈儏偱偼弌側偄偲偄偆偙偲偼丄僗僾儔僀僩RAM傊偺read偲write偑摨帪偵婲偙偭偰偄傞壜擻惈偑崅偄丅 僄儈儏偱偦傟傪嵞尰偡傞偙偲偼擄偟偄偐傜偹丅 偦傟偱丄SFL婰弎傪傛偔傛偔尒捈偟偰傒傞偲丄 PPU偺昤夋愝掕儗僕僗僞$2001:4偺僗僾儔僀僩桳岠柍岠愝掕儗僕僗僞偼偁傞傕偺偺丄 僗僾儔僀僩扵嶕帪偵偙傟傪嶲徠偟偰偄側偐偭偨丅 偙偺偨傔丄僗僾儔僀僩RAM傊偺僗僾儔僀僩扵嶕帪偺read偲丄DMA偐傜偺write偑廳側偭偰偟傑偄丄 write偑偆傑偔偄偐偢偵僑儈偲偟偰僗僾儔僀僩忣曬偑巆偭偰偟傑偆傛偆偩偭偨丅

丂僗僾儔僀僩僷僞乕儞僼僃僢僠帪偼懳嶔嵪傒偩偭偨偑丄 僗僾儔僀僩扵嶕帪偵傕僗僾儔僀僩柍岠帪偼僗僾儔僀僩RAM傊傾僋僙僗偟側偄傛偆偵廋惓偟偨丅 偙傟偵傛傝丄僑儈偑弌傞偙偲偼柍偔側偭偨丅

丵

仴 僞僀儈儞僌偺嵞尰偭偰擄偟偄丂2013/2/5

丂丂 丂丂惓忢側夋柺愗傝懼偊 |

丂PPU偲偼偪傚偭偲榖偑偢傟傞偑丄乽傾儖儅僕儘乿偼僇僗僞儉MMC3僠僢僾傪巊梡偟偰偄傞丅 僆儕僕僫儖偺MMC3偲堘偆偺偼丄CHR-ROM僶儞僋巜掕帪偵VRAM偺儈儔乕儕儞僌傕巜掕偝傟傞偲偄偆偲偙傠丅 幚憰偟偰傒偨偲偙傠丄塃偺摦夋偺傛偆偵丄夋柺愗傝懼偊帪偵杮棃偼崟偄夋柺偐傜僗僥乕僕夋柺偵愗傝懼傢傞偼偢偑丄 懠偺僷僞乕儞偑昞帵偝傟偰偄傞傛偆側晄嬶崌偑敪惗偟偨丅

丂嵟弶丄儈儔乕儕儞僌偺幚憰偑娫堘偭偰傞偺偐偲巚偄丄偄傠偄傠帋偟偰傒偨傕偺偺忬嫷偼曄傢傜偢丅 僄儈儏偱傕嵞尰偱偒側偄偺偱丄傆偲丄IRQ偵偮偄偰巚偄弌偟偨丅 偱丄帋偟偵IRQ傪敪惗偝偣側偄傛偆偵偡傞偲丄崟偄夋柺偐傜僗僥乕僕夋柺傊偺愗傝懼偊偑偱偒偨 乮偨偩偟IRQ偑擖偭偰偄側偄偺偱壓偺揰悢夋柺偑昞帵偝傟側偄乯丅

丂MMC3偺IRQ偵偮偄偰偼丄昤夋儔僀儞偱僇僂儞僞傪僨僋儕儊儞僩偟丄僛儘偵側傞偲IRQ偑敪惗偡傞丅 偙偺昤夋儔僀儞偺敾掕曽朄偑埆偔丄IRQ偺敪惗僞僀儈儞僌偑埆偐偭偨偺偑尨場偩偭偨丅

丂僪僉儏儊儞僩傪扵偟偰傒傞偲丄CHR_A12偱偄傠偄傠偲敾掕偟偰偄傞傛偆偵彂偐傟偰偁傞偑丄 崱夞偼乽if(chr_read & (CHR_A13==0b0)) f_draw := 1;乿偵偰昤夋儔僀儞偲敾掕偡傞偙偲偲偟偨丅 偮傑傝CHR_ROM傊偺Read傾僋僙僗帪偵僼儔僌傪棫偰丄 HBlank帪偵僼儔僌偑棫偭偰偄偨傜昤夋儔僀儞偲偟偰IRQ僇僂儞僞傪僨僋儕儊儞僩偡傞丅 偙傟傪幚憰偟偰丄傛偆傗偔惓忢偵僗僥乕僕夋柺傊偺愗傝懼偊偑偱偒傞傛偆偵側偭偨丅

丂偨偩偟偙傟偩偲侾僗僉儍儞儔僀儞暘丄IRQ偑抶傟傞傫偩傛偹乧丅

丵

仴 塀偟僗僾儔僀僩傒乣偮偗偨両丂2014/8/7

辈创创! 陡诿挪!? 泡棉!?

丂帺嶌僄儈儏偱儅儕僆俁偺摦嶌妋擣傪偟偰偰婥偯偄偨傫偱偡偗偳丄 僷僢僋儞僼儔儚乕偑搚娗偵塀傟偰側偄両

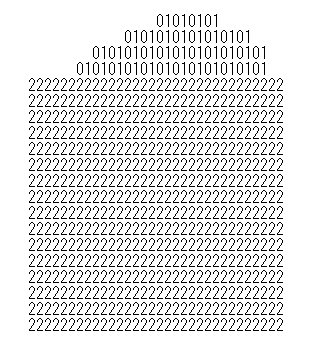

傾僩儕價儏乕僩懏惈

丂偲偄偆偙偲偱丄僗僾儔僀僩偲BG偺昤夋桪愭弴埵偑偍偐偟偄偺偐偲巚偄丄 僷僢僋儞僼儔儚乕晅嬤偺傾僩儕價儏乕僩懏惈傪僺僋僙儖偛偲偵僥僉僗僩弌椡偟偨傕偺偑偙偪傜丅 乽01乿偲偄偆偺偑僷僢僋儞僼儔儚乕偺摢偱丄 乽22乿偲偄偆偺偑搚娗偺強偵偁傞僗僾儔僀僩丅側傫偠傖偙傟偼丠

丂偙偺傾僩儕價儏乕僩懏惈傪尒傞偲丄價僢僩5偑棫偭偰偄傞偲昤夋偺桪愭弴埵偑BG傛傝傕掅偔側傞丅 偮傑傝丄BG僷僞乕儞偑柍偄強乮惵偄嬻乯偱偼僗僾儔僀僩偑昤夋偝傟傞偑丄 BG僷僞乕儞偑偁傞強乮搚娗乯偱偼偙偺僗僾儔僀僩偼昤夋偝傟側偄丅 偟偐傕丄偦偺僺僋僙儖偱昤夋偝傟傞僗僾儔僀僩偺桪愭弴埵偼ID偵傛偭偰寛傑偭偰偄偰丄 偙偺晹暘偱偼丄僷僢僋儞僼儔儚乕偺僗僾儔僀僩傛傝傕搚娗偺強偵偁傞乽22乿偺僗僾儔僀僩偺曽偑桪愭搙偑崅偄ID偲側偭偰偄偨丅

丂偳偆偄偆偙偲偐偲偄偆偲丄搚娗偺強偵BG偵塀傟傞僗僾儔僀僩傪抲偄偰丄

偦傟傛傝傕桪愭搙偑掅偄僷僢僋儞僼儔儚乕偺僗僾儔僀僩偑昤夋偝傟側偄傛偆偵偟偰偄傞柾條丅

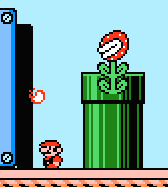

儅儕僆3丗BG僷僞乕儞偑偁傞売強偺搚娗

丂儅儕僆侾側傫偐偩偲丄扨弮偵搚娗偺弌岥偵偁偨傞偲偙傠偵偼BG僷僞乕儞傪抲偐側偄傛偆偵偟偰丄 搚娗偵擖傞僗僾儔僀僩偺昤夋傪BG偺棤懁偵偡傞偙偲偱搚娗偵塀偟偰偄傞丅 偟偐偟儅儕僆俁偩偲僗僥乕僕峔惉偑傛傝朙偐偵側偭偰偄傞偺偱丄 搚娗偺弌岥偵BG僷僞乕儞偑偁傞傛偆側応崌偩偲丄儅儕僆侾偺傛偆偵偼偄偐側偄丅 偦偙偱塀偟僗僾儔僀僩傪搚娗偺強偵抲偔偙偲偱丄 BG僷僞乕儞偑昤夋偝傟偰偄偰傕僗僾儔僀僩傪搚娗偵塀偡偙偲偑偱偒傞丅 側傫偲偄偆恊愗愝寁両

丂埲忋偺帠偑暘偐偭偨偨傔丄帺嶌僄儈儏偺僗僾儔僀僩昤夋晹暘傪廋惓偟偰偪傖傫偲僷僢僋儞僼儔儚乕偑搚娗偵塀傟傞傛偆偵側偭偨丅 HDL懁偱偼僄儈儏偲偼堎側傞幚憰傪偟偰偄偨偨傔丄弶傔偐傜偪傖傫偲塀傟傞傛偆偵側偭偰偄偨丅 偙偺晹暘丄僗僾儔僀僩昤夋張棟偑偪傖傫偲幚憰偝傟偰傞偐偳偆偐偺敾抐偵巊偊傑偡偹丅

丵

仴 儔僀儞僶僢僼傽傪巊梡偟側偄昤夋偵偮偄偰偺儊儌丂2018/9/8

丂夝愅帒椏偱偼丄PPU偺昤夋婡擻偵偮偄偰儔僀儞僶僢僼傽乮256僪僢僩暘乯偑偁傞偲偺婰弎偑尒摉偨傜側偄丅 偟偐偟恖偵傛偭偰偼儔僀儞僶僢僼傽偵昤夋偡傞偲偺愢柧傪偟偰偄傞応崌偑偁傝丄 峫偊偨寢壥傪偪傚偭偲儊儌偲偟偰巆偡丅

丂FPGA偱嶌偭偰傒偨偲偙傠丄PPU偺撪晹偱偼僗僾儔僀僩偺僷僞乕儞僔僼僩儗僕僗僞弌椡傪丄 僗僾儔僀僩偺桪愭弴埵夞楬偵婎偯偄偰弌椡偟丄BG偲偺桪愭搙偵墳偠偰昤夋偝偣偨丅 夝愅帒椏偵偁傞捠傝丄僗僾儔僀僩僷僞乕儞偼昤夋慜偺僗僉儍儞儔僀儞偱僼僃僢僠偡傞偨傔丄 昤夋儔僀儞帪偵BG偺昤夋偲摨帪偵僗僾儔僀僩傕昤夋偱偒傞丅 偮傑傝儔僀儞僶僢僼傽偼晄梫偱偁傞丅

丂傕偟僼傽儈僐儞偺PPU偱儔僀儞僶僢僼傽傪巊偆偲偟偨傜丄 341僒僀僋儖拞丄BG傪256僒僀僋儖偱昤夋偟丄8僪僢僩亊8僗僾儔僀僩傪64僒僀僋儖亄兛偱昤夋偱偒傞偺偱丄 僗僾儔僀僩偺桪愭弴埵夞楬偼晄梫偵側傞丅 偨偩偟偙偺応崌丄僗僾儔僀僩僷僞乕儞僼僃僢僠偲慜偺僗僉儍儞偱庢摼偟偨僷僞乕儞昤夋偑廳側傞偨傔丄 僗僾儔僀僩娭學偺僶僢僼傽儗僕僗僞偑梋暘偵昁梫偵側偭偰偟傑偆丅

丂偮傑傝丄昤夋夞楬偺愝寁偲偟偰丄儔僀儞僶僢僼傽偐桪愭弴埵夞楬偺偳偪傜偐傪慖戰偡傞帠偑峫偊傜傟傞偑丄 寢壥偲偟偰僼傽儈僐儞偱偼僐僗僩揑偵儔僀儞僶僢僼傽偼嵦梡偟側偐偭偨丄偲巚傢傟傞丅

丂堦曽丄PC僄儞僕儞偱偼儔僀儞僶僢僼傽傪巊梡偟偰偄傞傜偟偄丅 嵟弶偺256僒僀僋儖偱BG傪昤夋乮墶256僪僢僩儌乕僪帪乯偟丄 懕偔512僒僀僋儖偱32僪僢僩亊16屄乮嵟戝帪乯偺僗僾儔僀僩傪昤夋偟偰偄傞偲偺偙偲丅 僗僾儔僀僩偑僀儞僨僢僋僗弴偵昤夋偝傟傞偺偱偁傟偽丄 偍偦傜偔桪愭弴埵夞楬偼巊梡偟偰偄側偄偲峫偊傜傟傞丅 偮傑傝丄壙奿僐僗僩僶儔儞僗傪峫椂偡傞偲丄 僗僾儔僀僩偑懡偔側傞傎偳桪愭弴埵夞楬傛傝傕儔僀儞僶僢僼傽傪巊梡偟偨曽偑僐僗僩揑偵梷偊傜傟傞丄 偲偄偆壖愢偑棫偮丅

丂偪側傒偵NES on FPGA偱偼丄PPU弌椡傪VGA弌椡偵偡傞偨傔偺僼儕僢僾僶僢僼傽乮256僪僢僩亊2儔僀儞乯傪巊梡偟偰偄傞丅

偙傟偼丄PPU僪僢僩僋儘僢僋偑栺5.37MHz偱丄VGA僪僢僩僋儘僢僋偑25.2MHz偲偄偆嵎乮栺係攞乯傪媧廂偡傞偨傔丅

PPU偑僶僢僼傽A偵1儔僀儞乮256僪僢僩乯昤夋偟偰偄傞娫偵丄

VGA偑僶僢僼傽B偐傜2儔僀儞乮512僪僢僩亊2儔僀儞乯弌椡偡傞丅

昤夋媦傃弌椡偑廔傢偭偨傜僶僢僼傽AB傪BA偵愗傝懼偊傞乮僼儕僢僾乯丅

PPU昤夋梡偲偟偰儔僀儞僶僢僼傽傪巊梡偟偰偄傞傢偗偱偼側偄偙偲偵拲堄丅